Hello! I am Abid

I'm a Software Firmware Engineer currently pursuing a Master's in Computer Science at Arizona State University. With a strong foundation in software development, I seamlessly blend my educational pursuits with practical experience. Prior to my master's program, I worked at Hewlett Packard, where I led and managed the development, testing, and maintenance of IO modules. Proficient in languages like Java, JavaScript, C/C++, and Python, I excel in crafting intricate applications and optimizing performance. Additionally, my coursework and projects have sharpened my skills in distributed systems, full stack development, and real-time embedded systems.

Furthermore, my undergraduate background in Electronics and Communication Engineering complements my software proficiency. I serve as a conduit between the software and hardware worlds, leveraging my expertise to design hardware using Verilog, synthesize FPGA solutions, and navigate embedded systems intricacies. This integrated perspective allows me to approach problems holistically, ensuring comprehensive and effective solutions.

Experience & Education

Projects

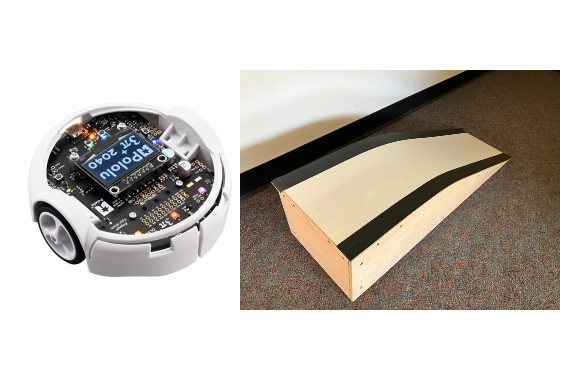

Hill Climb

Executed a robotic project utilizing the Pololu 3pi+ 2040 robot and Raspberry Pi RP2040 microcontroller. Integrated obstacle detection, line sensing, feedback control, accelerometer, and gyroscope. Engineered a Lingua Franca-based finite state machine for efficient ascent, summit detection, directional adjustments, and safe descent.

Fully Homomorphic Encryption

Conducted a comparative analysis of Fully Homomorphic Encryption (FHE) using Microsoft SEAL and OpenFHE libraries. Implemented FHE schemes, assessed runtime efficiency, and explored overheads. Highlighted superior performance of OpenFHE in implementing FHE schemes.

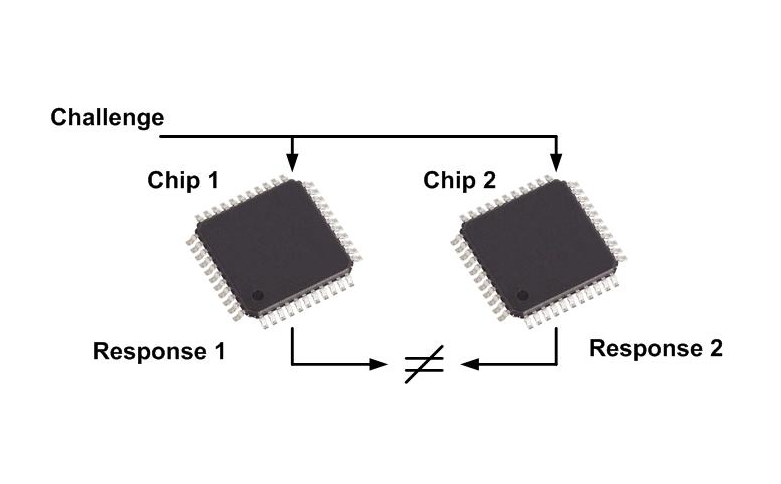

Physical Unclonable Functions: Arbiter PUF and RO PUF

Implemented and documented a hardware security project on Physical Unclonable Functions (PUFs), focusing on Arbiter PUF and Ring Oscillator PUF. Achieved single-chip Hamming distances of 49.10% and 41.30% respectively.

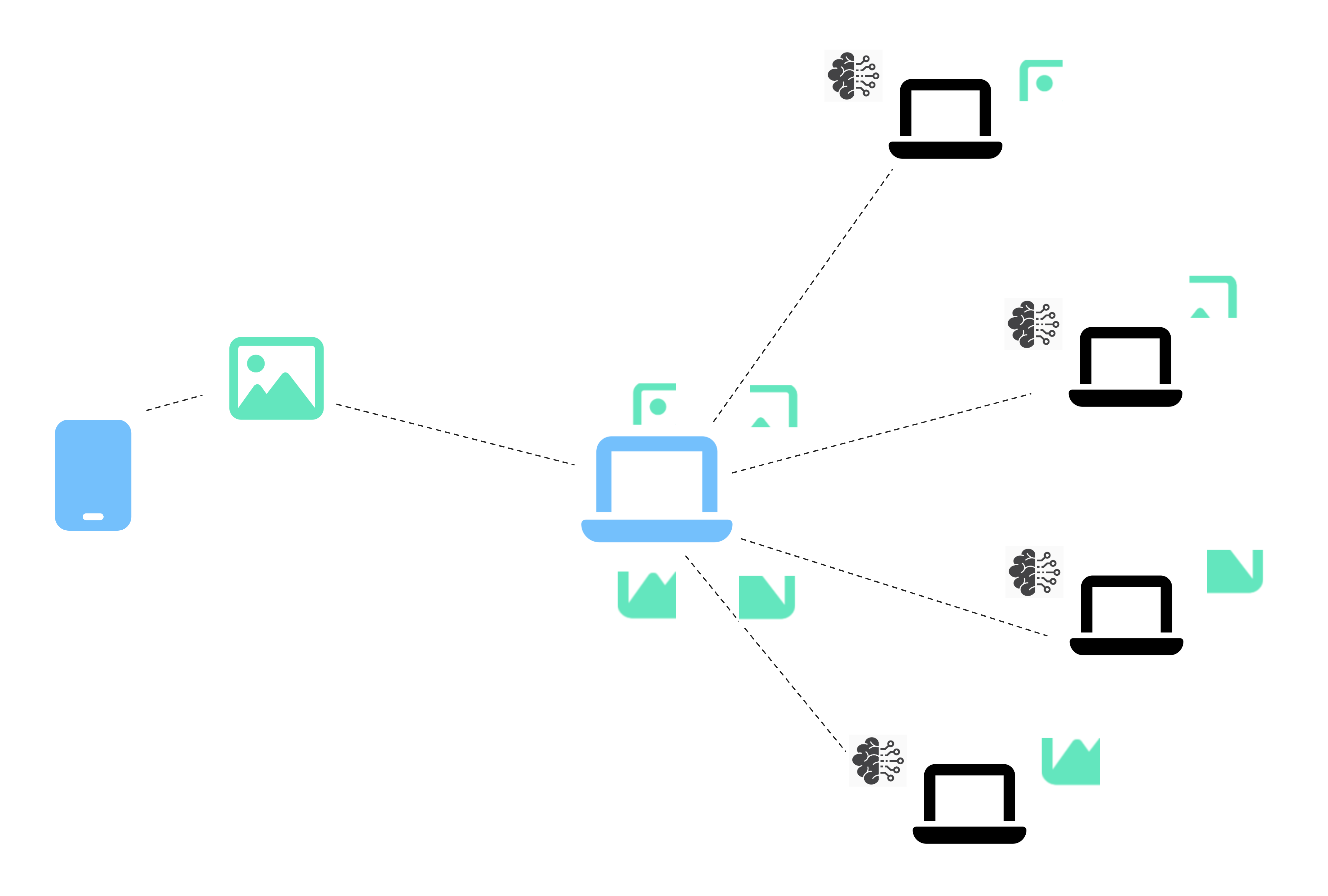

Enhancing Edge Device Image Classification: Seamless Integration in Mobile Computing

Implemented server-side image classification for edge devices using Android app and CNNs. Real-time handwritten digit classification achieved with 80.34% accuracy. Demonstrated transformative potential of server integration in mobile computing.

Optimizing Hardware Implementation of the Exponential Function: A Deep Dive

Explore hardware optimization techniques for computing the exponential function, crucial in machine learning for functions like softmax. Implemented Verilog on an FPGA platform to improve performance and efficiency. Learn more about the project's strategies and outcomes in the project.Languages and Tools 💻